MIPS延迟槽技术

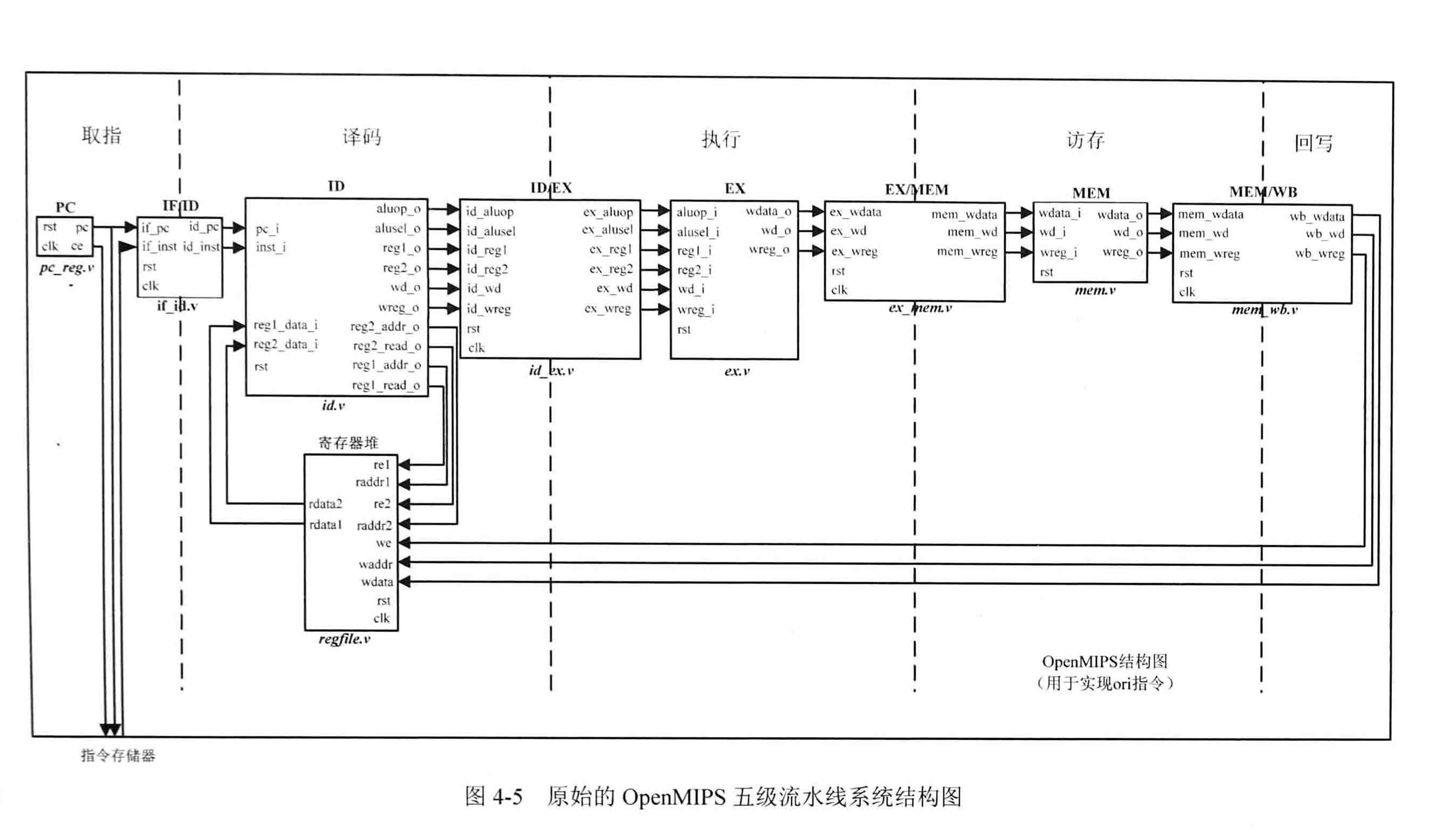

先放一张原始的MIPS流水线图,图片来自雷思磊的《自己动手写CPU》

目前流水线是按顺序执行,没有加入跳转语句的数据通路,假设我们在**“执行阶段”**才知道比较跳转指令beq需要跳转,那么此时已经在取指、译码的两条指令会无效,下一个时钟周期需要把它们清空,于是流水线出现两个周期的气泡。跳转前的状态如下:

······

beq $t1,$t2,label #执行阶段

ori $3,$3,0x8 #译码阶段,下一刻清空

ori $3,$3,0x9 #取指阶段,下一刻清空

······

label:

or $4,$9,$0 #下一刻取指

······

为了提高流水线的效率,避免气泡,MIPS的架构做了两个改进: 1、分支指令的判断提前到译码阶段,一部分比较逻辑在译码时完成,而不用等到执行阶段。这样可以少一个气泡。 2、索性不清空取指阶段指令,让它继续执行,反正下一个指令是跳转指令,只要有个标记知道它是“多出”的指令,称为“延迟槽指令”。所以把转移指令后面的指令位置称为“延迟槽”。这样流水线就没有气泡了。

如果指令不跳转,那么正好执行下一条;如果跳转指令不久又跳回来,那么从原来跳转指令下两条开始执行,比如上面的ori $3,$3,0x9,如果不跳回来,那么相当于白运算了一次,总体上看,还是很划算的。修改后的跳转前状态:

······

beq $t1,$t2,label #译码阶段就可判断

ori $3,$3,0x8 #取指阶段,下一刻译码

ori $3,$3,0x9 #如果跳回来,这里开始取指

······

label:

or $4,$9,$0 #下一刻取指

······

具体实现增加的数据通路如下:

细节还得参看verilog代码,先有个大概轮廓吧。