Chisel 从入门到放弃

吃鸡卷王钦哥在暑假期间入坑Chisel,仍然吃鸡,已然抛弃羽毛球。现在已经可以用Chisel替代verilog做工程项目,这转身真是迅速!诚邀钦哥总结一路踩过的坑,因此有了这篇汇总博文。

官网

1. GitHub - chipsalliance/chisel3: Chisel 3: A Modern Hardware Design Language

2. Chisel/FIRRTL: Introduction (chisel-lang.org)

3. Chisel 中文社区 (chiselchina.com)

很多问题在上述链接 2 都能解答,主要在 Resource 和 Cookbooks 目录下,以下给出 General Cookbook 目录下一个常见问题的解答 (很可能遇到的 , 部分位的赋值问题):

Chisel3 does not support subword assignment . The reason for this is that subword assignment generally hints at a better abstraction with an aggregate/structured types, i.e., a

Bundleor aVec.If you must express it this way, one approach is to blast your

UIntto aVecofBooland back:

import chisel3._

class Foo extends Module {

val io = IO(new Bundle {

val in = Input(UInt(10.W))

val bit = Input(Bool())

val out = Output(UInt(10.W))

})

val bools = VecInit(io.in.asBools)

bools(0) := io.bit

io.out := bools.asUInt

}

环境配置

1. intellij IDEA 下载

Download IntelliJ IDEA: The Capable && Ergonomic Java IDE by JetBrains

选择社区版本够用了

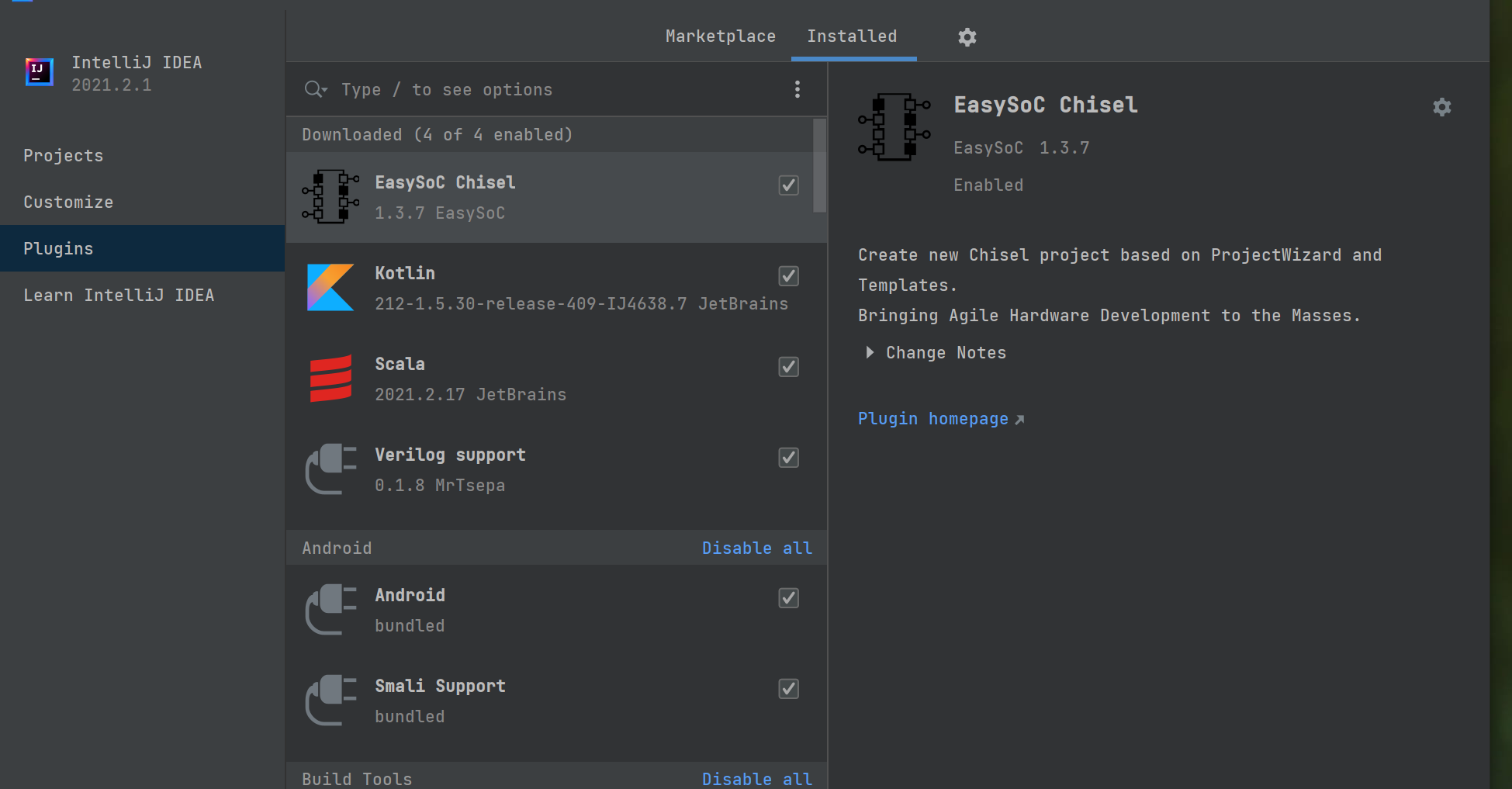

2. 插件安装

chisel 插件提供了 Chisel Project 模板,可以快速配置 scala 版本和 sbt(scala build tool)

3. 工程创建

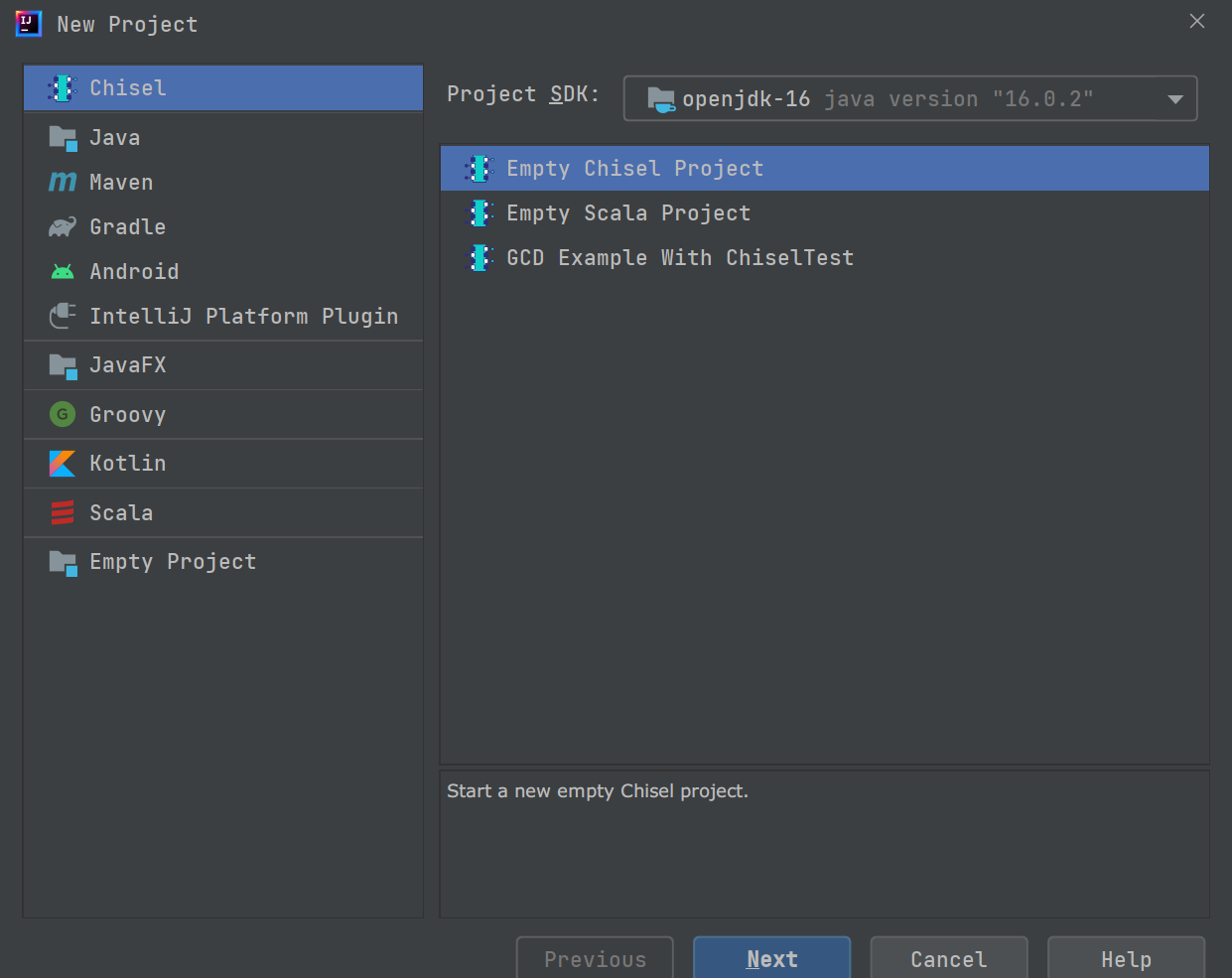

路径: project - new project - chisel - empty chisel project,假如没有 SDK 就安装图示的 openjdk.

图中的 GCD Example 是官方提供的一个样例程序,同时提供了设计和内建测试的代码

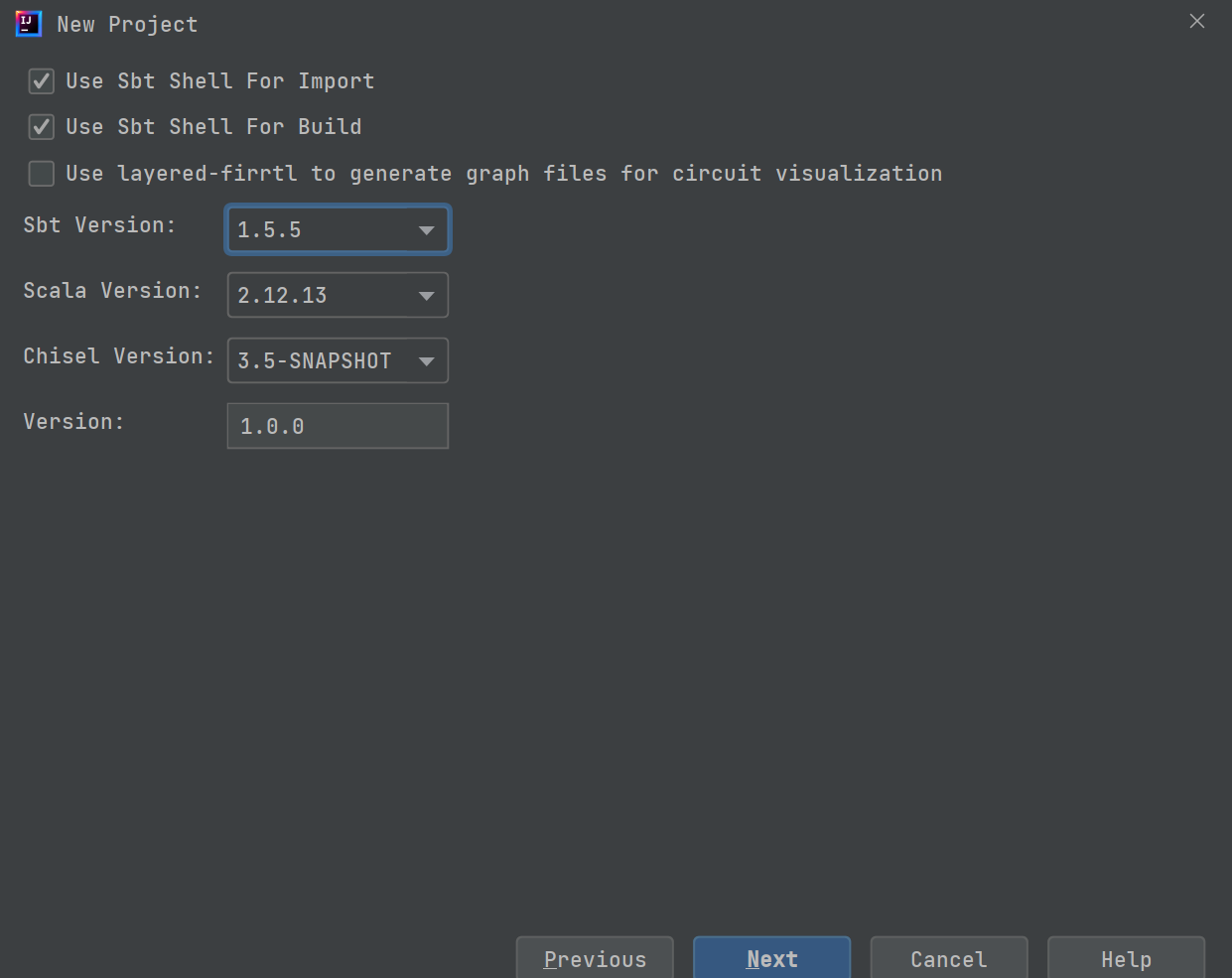

目前个人的配置如上,sbt 版本最好就是按照官网版本提供的,否则编译过程中报奇怪的错很难界定原因.假如后续 chisel 更新之后代码莫名跑不通了,可以参照官网的说明以及样例程序,检查自己的工程中 sbt 或者 scala verision 是否过时了

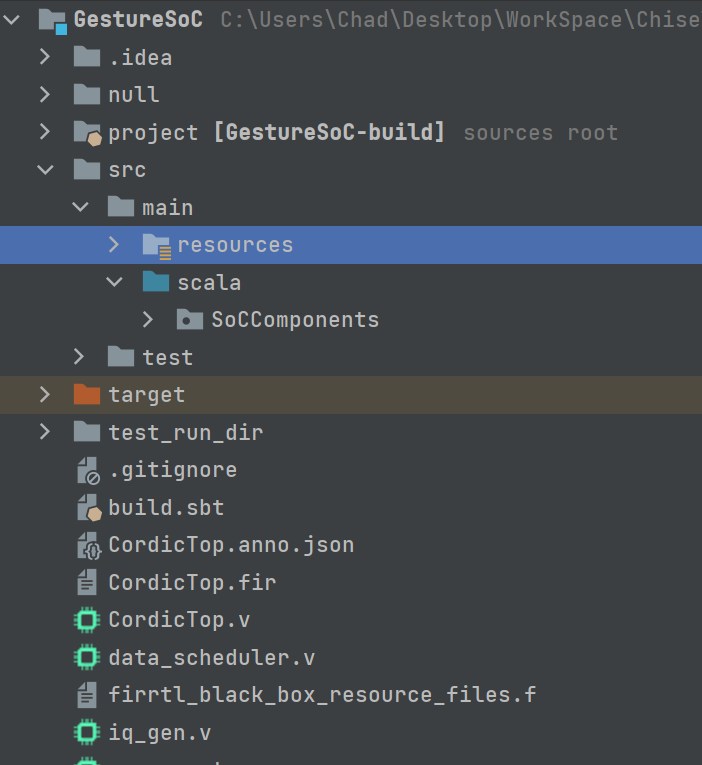

4. 文件结构 & chisel 设计模板创建

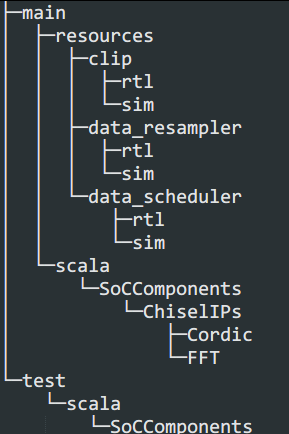

上图给出了工程文件的结构示意图, 主要关注的是 /src 路径下的文件,以及根目录(Project)下的 /test_run_dir 和 生成的 .v 文件(编译通过才有),其中 /src 文件夹下的主要内容如下图

-

/src/main/resource文件夹存放来自外部的 verilogIP,此路径是 chisel 默认的 blackBoxResource(即此处的 verilogIP) 存放路径,以下给出 1 个示例class data_scheduler(DI_W: Int, DO_W: Int) extends BlackBox with HasBlackBoxResource with ParamTable { val io = IO(new Bundle() { val params_intl_ch_num = Input(UInt(2.W)) val params_cpi = Input(UInt(SLOW_TIME_CNT_W.W)) val params_frame_interval = Input(UInt(SLOW_TIME_CNT_W.W)) val params_samples_per_tr = Input(UInt(FAST_TIME_CNT_W.W)) val params_total_samples_per_ch = Input(UInt(CH_SAMPLE_CNT_W.W)) val params_fft_in_inv_order = Input(Bool()) ... //按照verilogIP端口声明所有的变量 //这里声明的变量名就是chisel例话IP时候的端口名 //另外,chisel并不会检查verilogIP的端口与这里声明的变量是否同名 //因此,这里声明的变量名一定要跟verilogIP端口名完全对应, //否则会出现"port nof found"错误 }) addResource("/data_scheduler/rtl/data_scheduler.v") //默认目录为/resource,这里非默认路径,需要进一步指明文件位置 } -

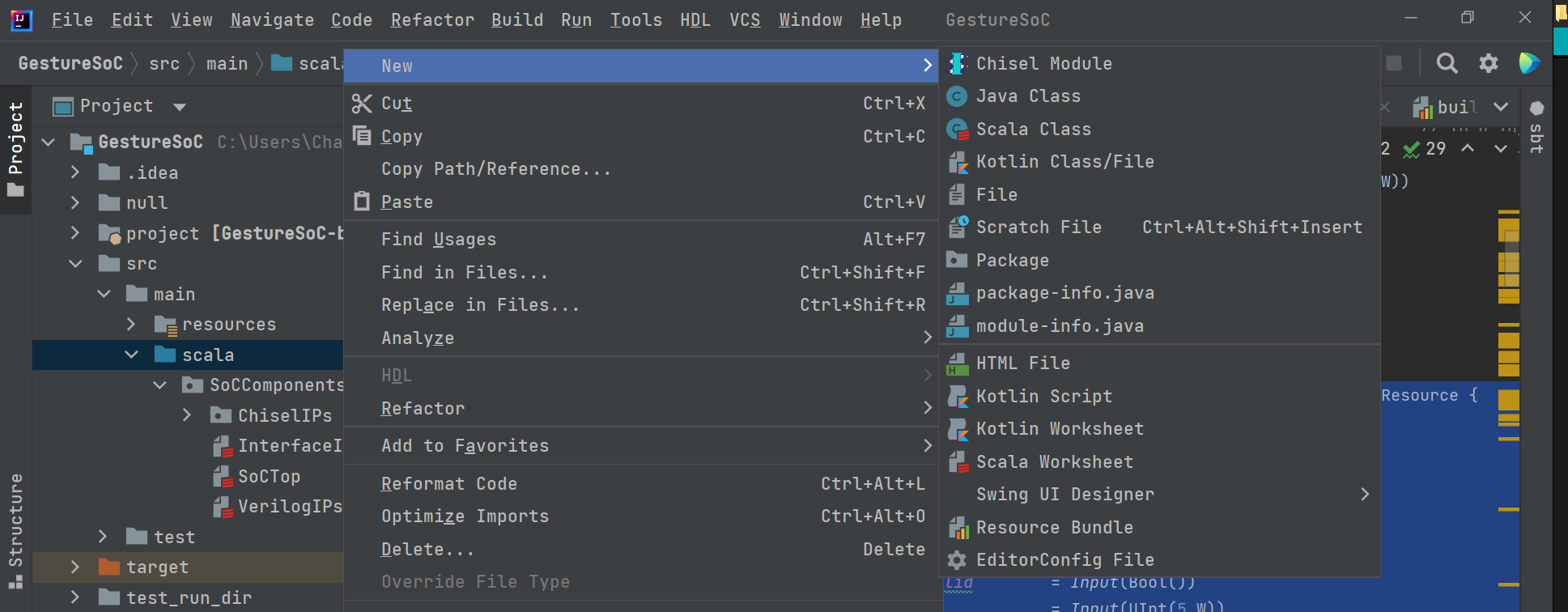

/src/main/scala路径下存放设计文件 假如设计文件分类较多,可以采用 package 来管理,如下图所示

在创建了 Package 之后,例如上图的 SoCComponents,类似地,选中该 Package,右键菜单可以进一步创建 Package,或者是直接就创建一个 Chisel Module 的模板.

5. 生成 verilog

参照官网教程完成设计之后,可以采用如下语句生成 verilog(当前的最新版本),这个生成 verilog 的方法官方一直在迭代,网上的博客很多给的是比较落后的方法

object SoCGen extends App {

val verilogString = (new chisel3.stage.ChiselStage).execute(Array(""),

Seq(ChiselGeneratorAnnotation(() => (new SoCTop))))

//SoCTop是设计文件(Class)

/*

val targetDir = "test_run_dir/SoCTop"

(new ElkStage).execute(

Array("-td", targetDir),

Seq(ChiselGeneratorAnnotation(() => new SoCTop)) //这是生成架构图的,可以先不用

)*/

}

参考博客

入门

以下博客给的生成 verilog 方法基本都已过时 !

如何在 windows 上搭建 chisel 环境(除了 chisel,作者还提供了很多其他数字设计内容)

初学 Chisel 语言,看这篇就够了:最方便简洁的入门资料整理 - 知乎 (zhihu.com)

Introduction | Tour of Scala | Scala Documentation (chisel 内语法看不懂时的参考,且有些 scala 语法提供的语法糖对于减少设计也有帮助))

进阶

用 Chisel 快速搭建 FFT 流水线电路 - 知乎 (zhihu.com)

第二十二章 Chisel 基础——多时钟域设计__iChthyosaur 的博客-CSDN 博客

【Chisel 学习笔记 1】隐式参数(比较高级的传参,可以略过)

ChiSel 学习笔记 - (提供了一个端口列表参数化的方法)

算法函数_Chisel 实践——利用 CORDIC 算法计算对数函数_街机时代的博客-CSDN 博客

高阶应用

chisel 高阶用法简介--rocket-chip generator - 知乎 (zhihu.com)

(27 封私信 / 80 条消息) 如何深入理解 rocket-chip core 的代码? - 知乎 (zhihu.com)

RocketChip 学习笔记系列 - 知乎 (zhihu.com)