ADC(三)Guard ring

Guard ring 是用来隔离电路的,特别是模拟模块和数字模块,灵敏放大模块和高功率模块等。

一开始画单元模块的时候,一直在纠结需不需要画Guard ring,或者说多大的模块需要才需要画Guard ring?上学期画过简单的反相器,两个黄色的框就是Guard ring ,外边是Nwell接高电平,里边是Psub接低电平。同时Pmos外边也围了Nwell、Nmos外边也围了Psub。

小小一个反相器,要围那么多东西,这要多消耗面积啊?上学期简单的课程作业可以这么玩,现在可是要流片呀,而且这么多元件,每个都这么画,得多麻烦!那么这Nwell、Psub、Guard ring 包围电路的尺度要多大才合适呢?这个问题一直困扰了我很久。

小小一个反相器,要围那么多东西,这要多消耗面积啊?上学期简单的课程作业可以这么玩,现在可是要流片呀,而且这么多元件,每个都这么画,得多麻烦!那么这Nwell、Psub、Guard ring 包围电路的尺度要多大才合适呢?这个问题一直困扰了我很久。

一、摸石头过河

预期停留在想,不如先做做看,还是从最简的反相器开始,先保证功能,过DRC和LVS,然后再想办法减小面积。

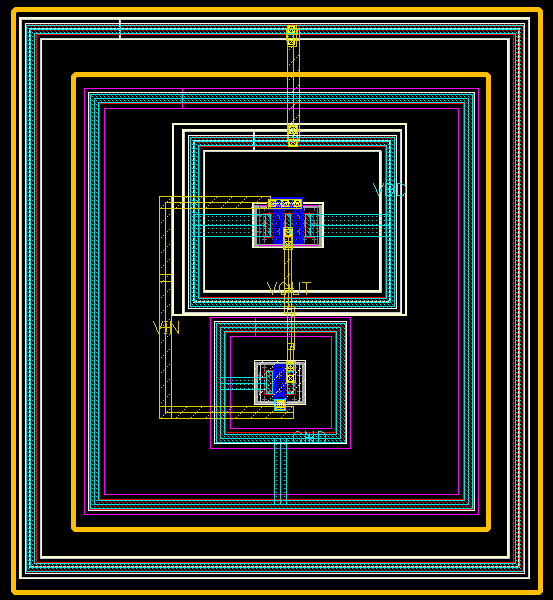

这是第一版反相器,暂时没画Guarding ring。然后答疑的时候,老师说我画得太宽松,可以再紧凑一些,因此有了第二版,只要drc没有报错,就一直减小间距,这一招在后续的单元里屡试不爽,都快把间距的drc背下来了,熟练之后drc一遍过,我成了活生生的“drc”。

这是第一版反相器,暂时没画Guarding ring。然后答疑的时候,老师说我画得太宽松,可以再紧凑一些,因此有了第二版,只要drc没有报错,就一直减小间距,这一招在后续的单元里屡试不爽,都快把间距的drc背下来了,熟练之后drc一遍过,我成了活生生的“drc”。

再给老师查看效果,老师说还可以把外面的Nwell和Psub去掉,可以参考标准单元库,下图是用标准单元库搭一个延时模块,确实没有Nwell和Psub。

再给老师查看效果,老师说还可以把外面的Nwell和Psub去掉,可以参考标准单元库,下图是用标准单元库搭一个延时模块,确实没有Nwell和Psub。

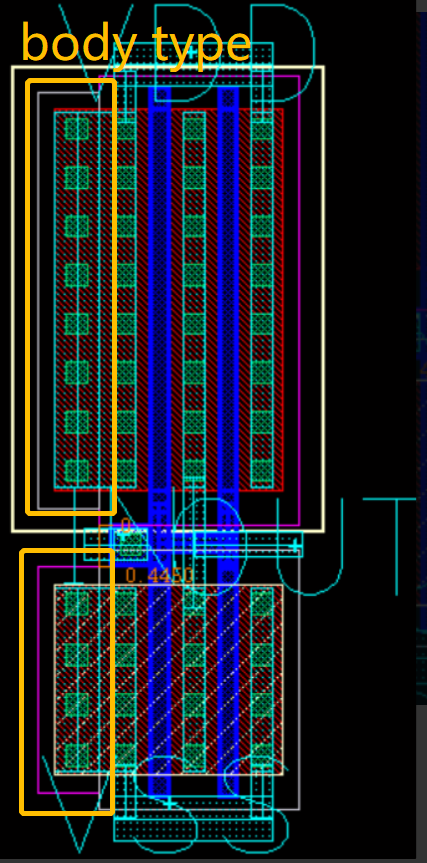

于是有了反相器的第三版,但需要注意的是,去掉之后需要添加单元的body type(选中,Q,parameter,bodytie_typeR),表示衬底接VSS或VDD,不然drc会报错(不过后面总是要围Nwell或Psub的,所有暂时忽略也行)

于是有了反相器的第三版,但需要注意的是,去掉之后需要添加单元的body type(选中,Q,parameter,bodytie_typeR),表示衬底接VSS或VDD,不然drc会报错(不过后面总是要围Nwell或Psub的,所有暂时忽略也行)

这样操作之后,面积从最初的16um×6um缩小到8×3um,变为原来的1/4。

这样操作之后,面积从最初的16um×6um缩小到8×3um,变为原来的1/4。

二、熟能生巧

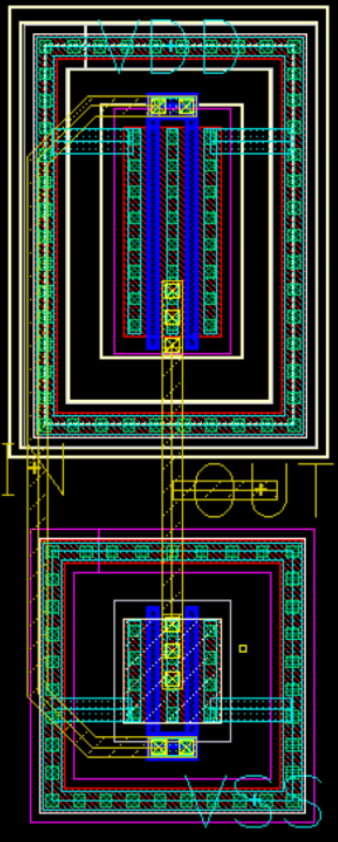

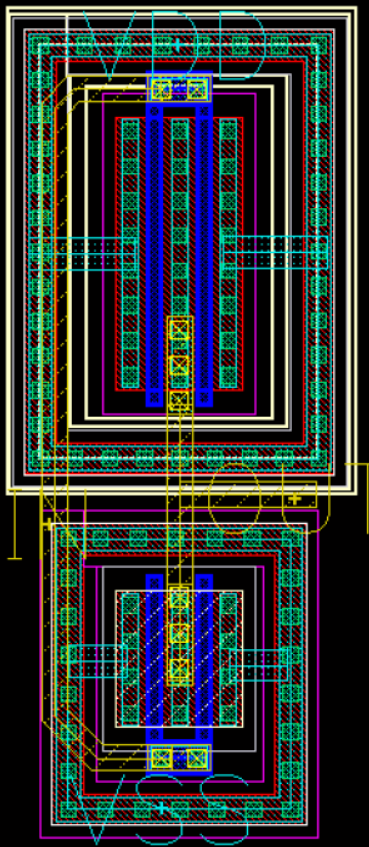

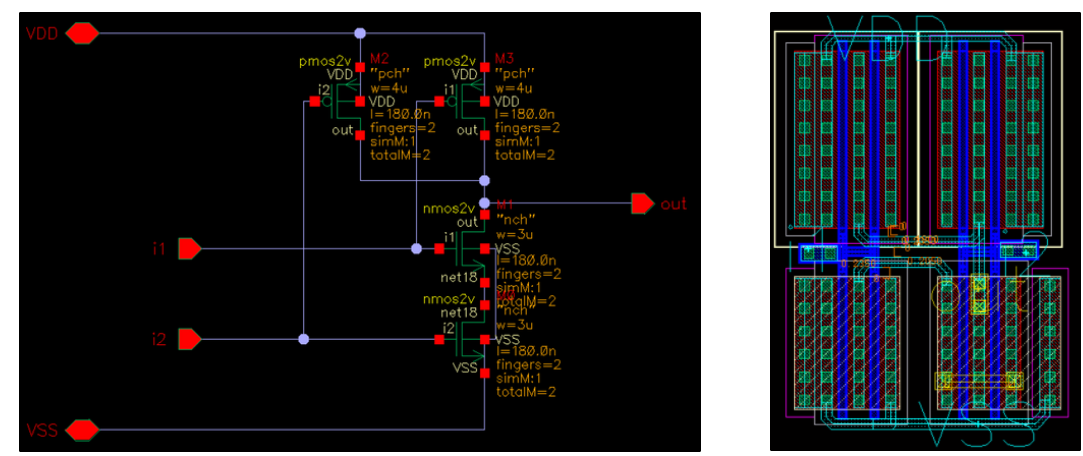

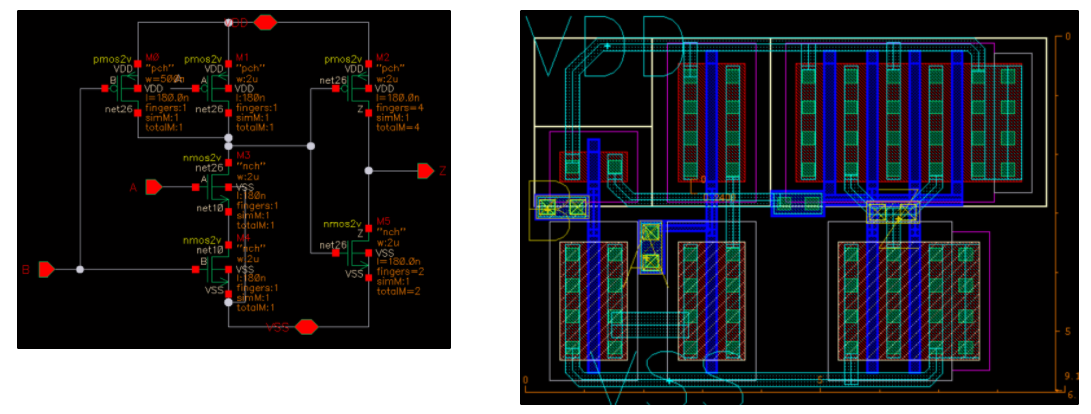

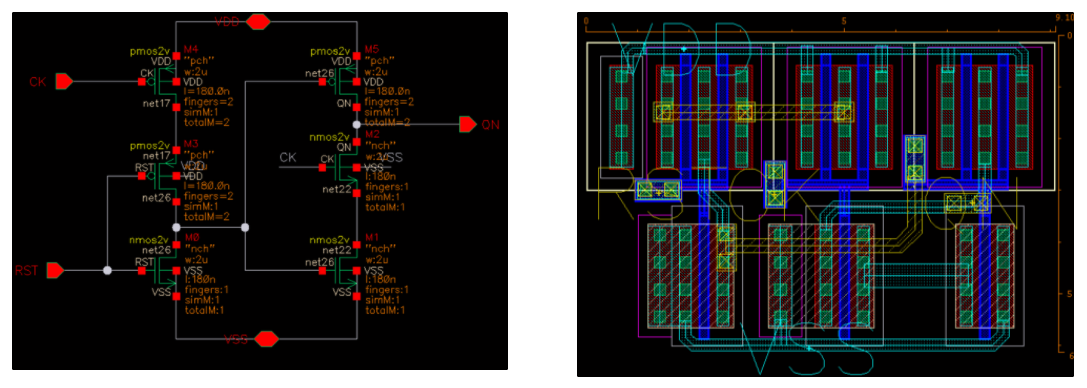

有了这个技巧之后,接着画了几个基本单元:NAND、AND、真单相时钟(TSPC_RC)

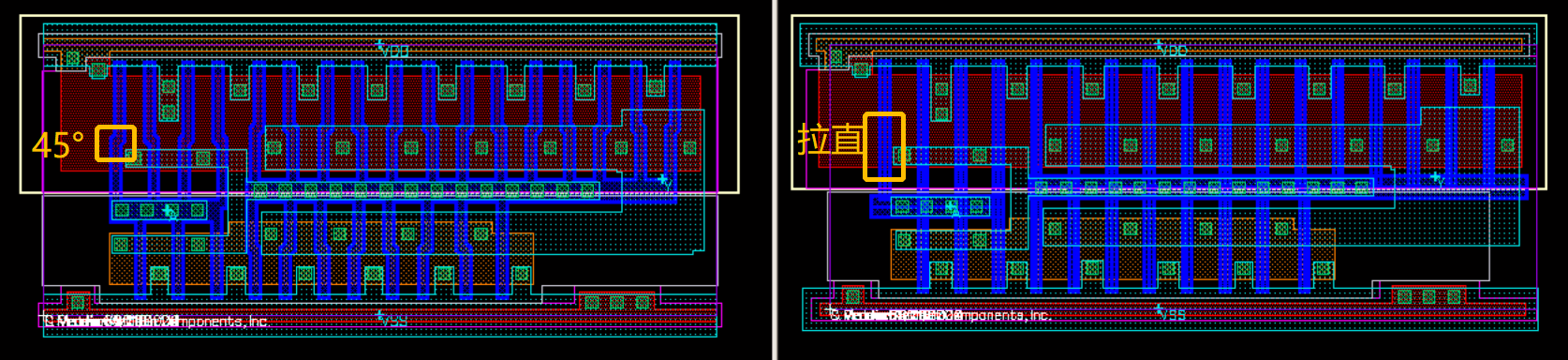

中间还有个小插曲,有一个clkbuf的模块是库里提供的,但是它的栅极画得太紧凑,导致有45°的转角,这在pex提取寄生参数后仿的时候会报错,因此需要手动修改单元库的版图,先打散,然后调整。

中间还有个小插曲,有一个clkbuf的模块是库里提供的,但是它的栅极画得太紧凑,导致有45°的转角,这在pex提取寄生参数后仿的时候会报错,因此需要手动修改单元库的版图,先打散,然后调整。

三、柳暗花明

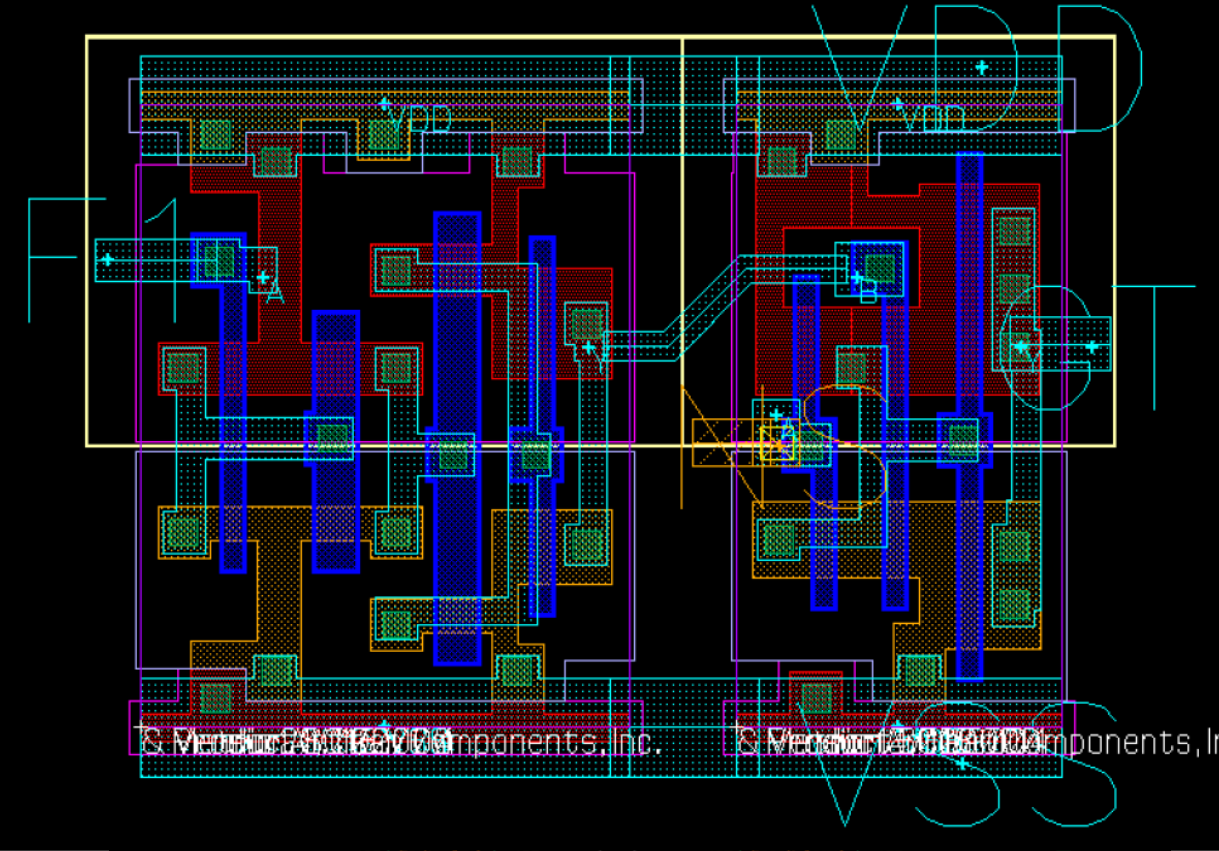

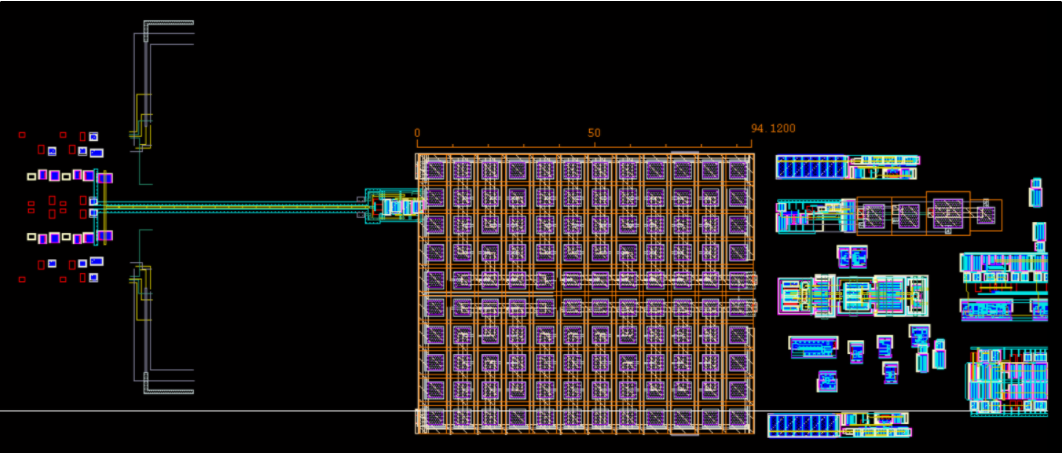

但何时加Guard ring的问题还是没有解决,因为所有的基本单元和模块目前都没有加ring,知道需要拼总版的时候,思路才清醒起来。看这一地鸡毛的总版,可以想象我当时内心是多么混乱。总版的好处是可以看到各个模块的相对大小,有些模块可以合在一起加ring,有些单个模块就比较大,单独加ring。

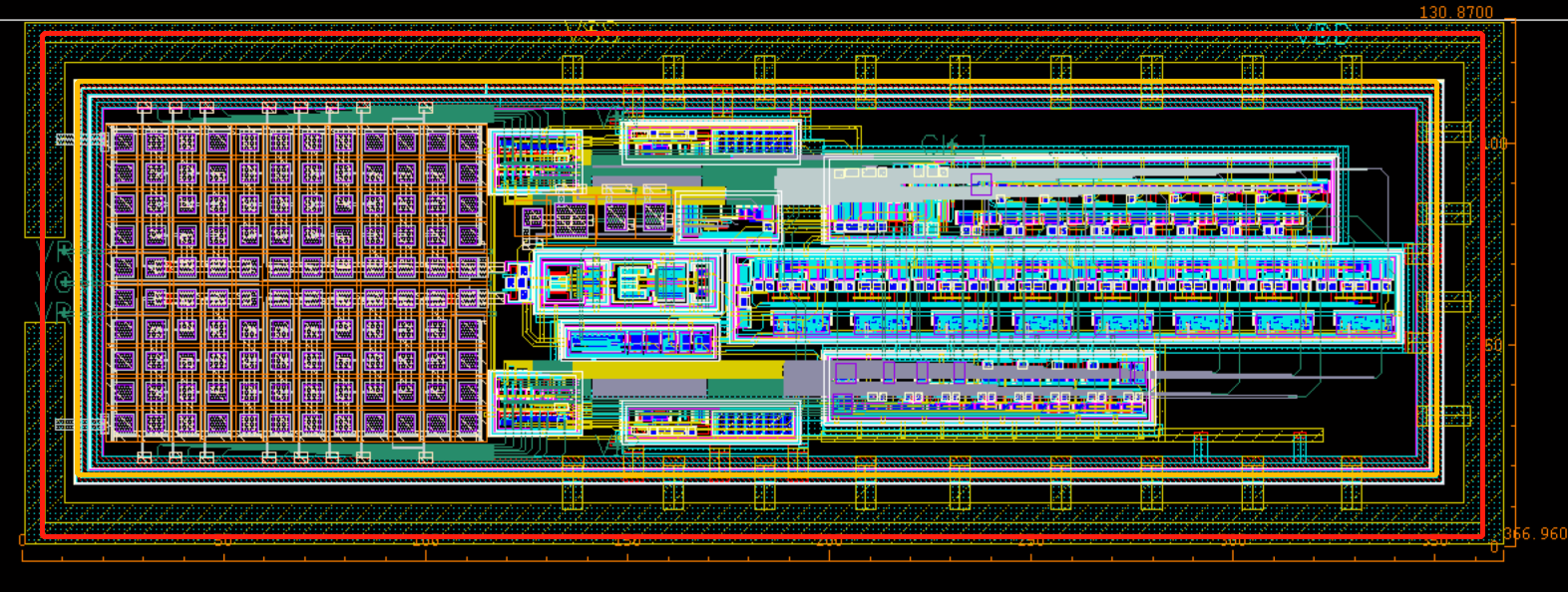

总版大概布局好位置之后,将小的模块拼紧凑一下,然后用Guard ring 围起来,看起来也不那么凌乱。图中分别标出了各个模块的作用,外部都用Guard ring 分隔开,更具整体性,这种自底向上封装,自顶向下布局让版图颇具美感。

最后会在最外面加上大大的Guard ring(图中黄色框),并在外面围一圈厚厚的VSS和VDD(图中红色框),用来隔离保护:

至此,从完成了反相器到ADC的飞跃。万丈高楼平地起,一夜暴富也意味着一夜暴穷,一点一滴的积累才是正道。