ADC(零)天线错误

上文ADC笔记(一)说已经完成了说有版图,没想到8月底经历了一场刺激的debug之旅,差点崩溃。

一、溃不成军

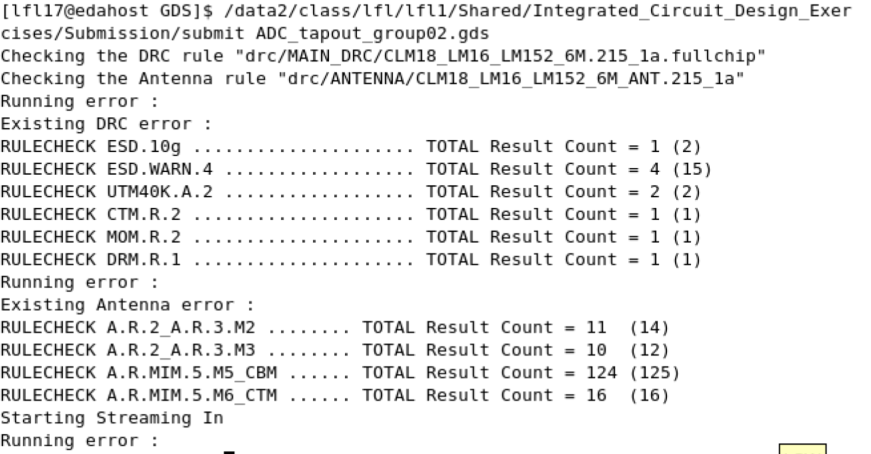

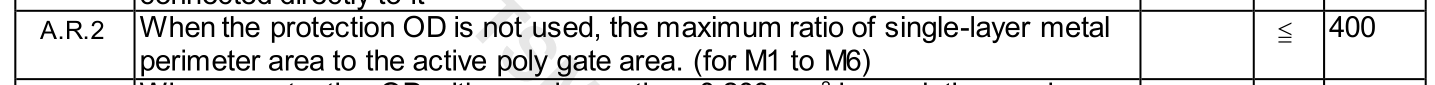

版图gds文件的提交在8月底,当时以为传个gds文件就可以交差了,没想到提交的时候,还要自动做两个drc检查:

- 全芯片drc:CLM18_LM16_LM152_6M.215_1a.fullchip

- 天线检查:CLM18_LM16_LM152_6M_ANT.215_1a

当时上百个错误如下,“我看不懂,但大受震撼”。那时在深夜,突然体会到《西游记》最后一难——通天河遇鼋湿经书。本以为历经千难,完结课程,没想到最后还来这一出,之前不知道还要做着两个检查,知道ddl才告诉我们,打得我措手不及,不讲武德呀!

上面这些错误,天线部分不能有,防止制造过程中破坏器件;fullchip中的ESD.10g、UTM40K.A.2不能有。那夜无眠,为之奈何?

二、重振旗鼓

第二天约队友一起debug,从午饭开始到晚上11点半,查文档、搜论坛、问助教、问同学、问工程师,最终有一些进展,但还是没有完全解决。射频卷王鑫韬非常给力,几次在我要放弃不干的时候给信心。我们互相换着debug,进展也就是我换成ESD.10g,他换成天线的时候取得的,又想起那句话“一个人走得快,一群人走得远~”。

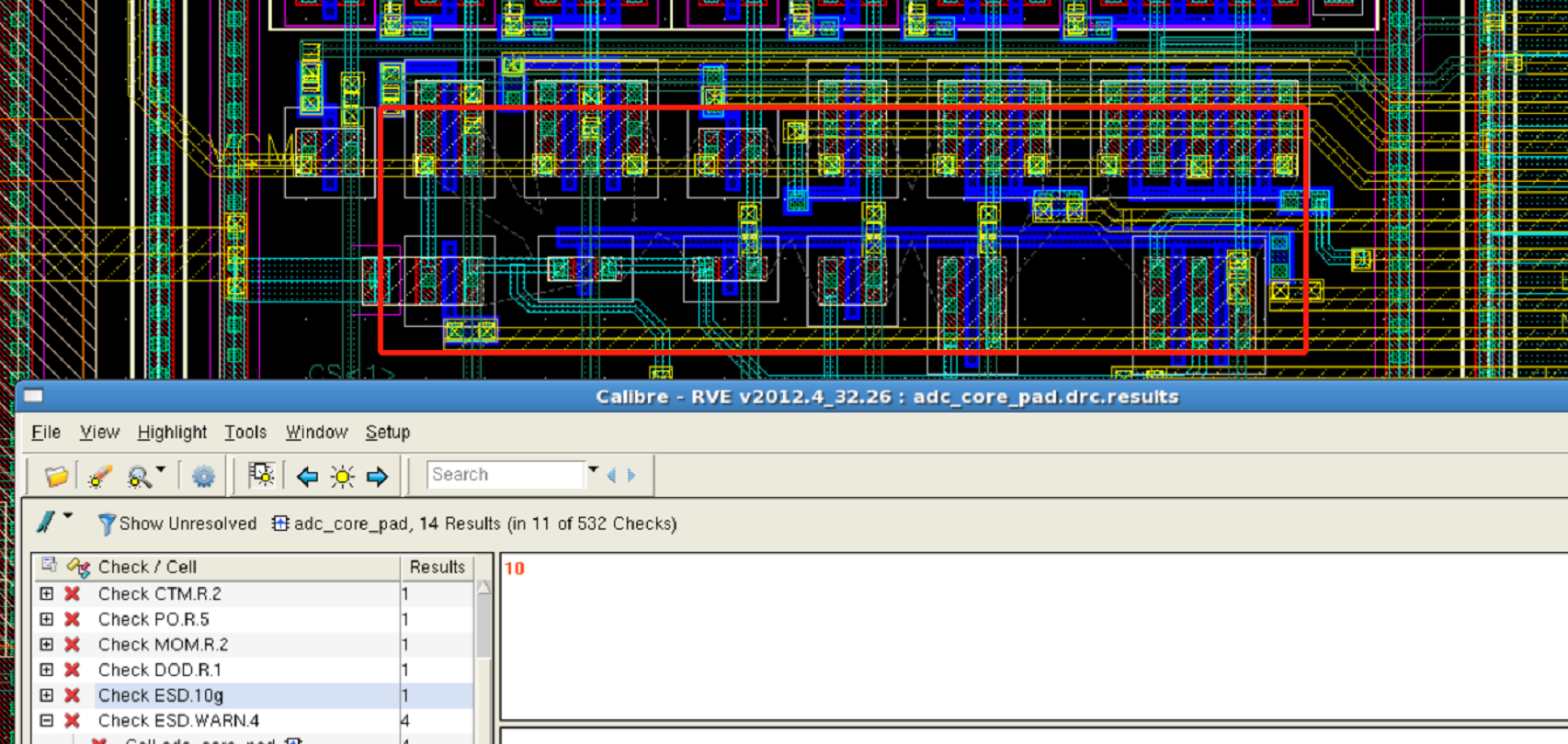

Bug1. ESD.10g

ESD.10g 如下面红框所示,一堆乱七八糟的虚线乱闪,甚是心烦。

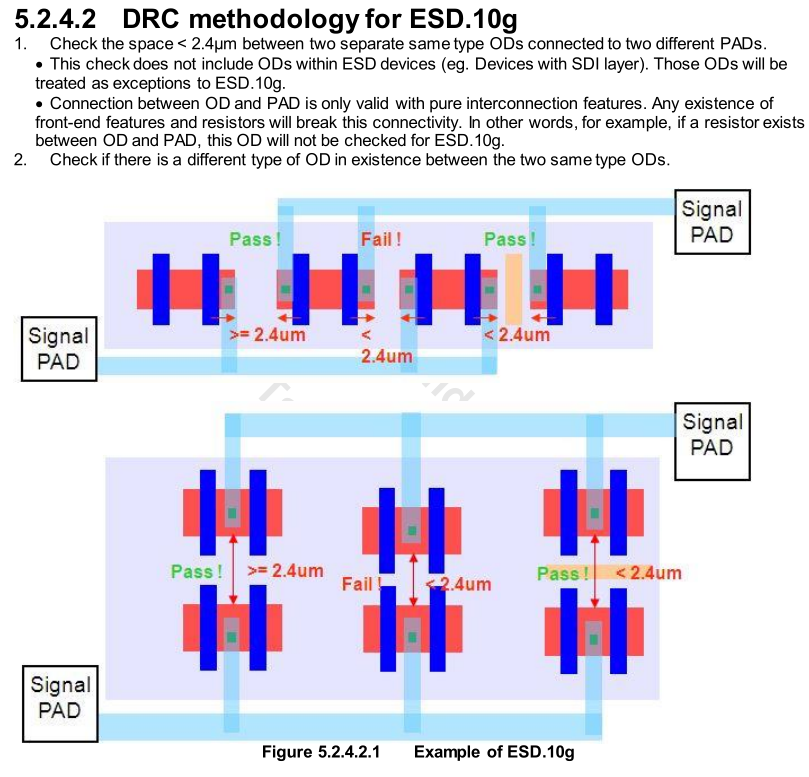

文档上说,连接不同PAD的有源区(OD)的距离要大于2.4um,这部分有差分输入电压(VIP)、共模电压(VCM)、最大电压(VRP)、最小电压(VRN)这4个PAD,当时布局的时候想省面积,摆的有些紧凑,没想到会因为要接PAD而翻车。

文档上说,连接不同PAD的有源区(OD)的距离要大于2.4um,这部分有差分输入电压(VIP)、共模电压(VCM)、最大电压(VRP)、最小电压(VRN)这4个PAD,当时布局的时候想省面积,摆的有些紧凑,没想到会因为要接PAD而翻车。

知道原因之后,改起来就有了方向:区分各个pad连接的晶体管,然后将它们分开至大于2.4um。比较前后两个电容开关模块(DA_SW)的版图,看到两个黄框分别隔开了不同pad连接的有源区。

Bug 2. A.R.MIM(MIM电容天线错误)

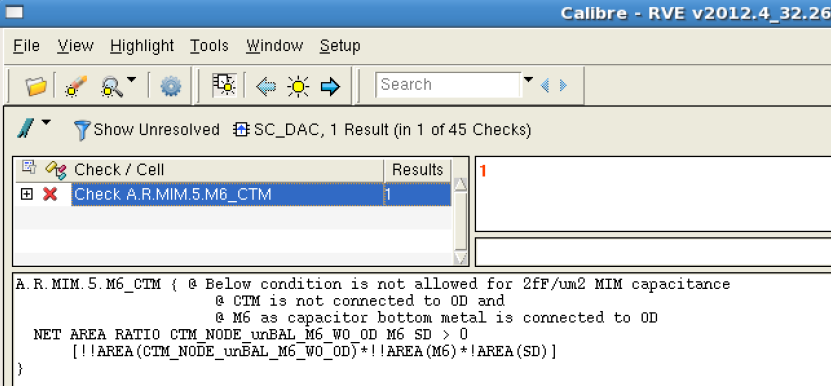

早知道MIM电容怎么麻烦,我就用MOM电容了。报了一堆错,不忍直视,错误提示如下:

单词我都懂,但连起来就不懂了,CTM(cap top metal)需要接到OD(有源区)?我读书少,有源区不是VSS/VDD吗,接上去不是影响功能吗?!

单词我都懂,但连起来就不懂了,CTM(cap top metal)需要接到OD(有源区)?我读书少,有源区不是VSS/VDD吗,接上去不是影响功能吗?!

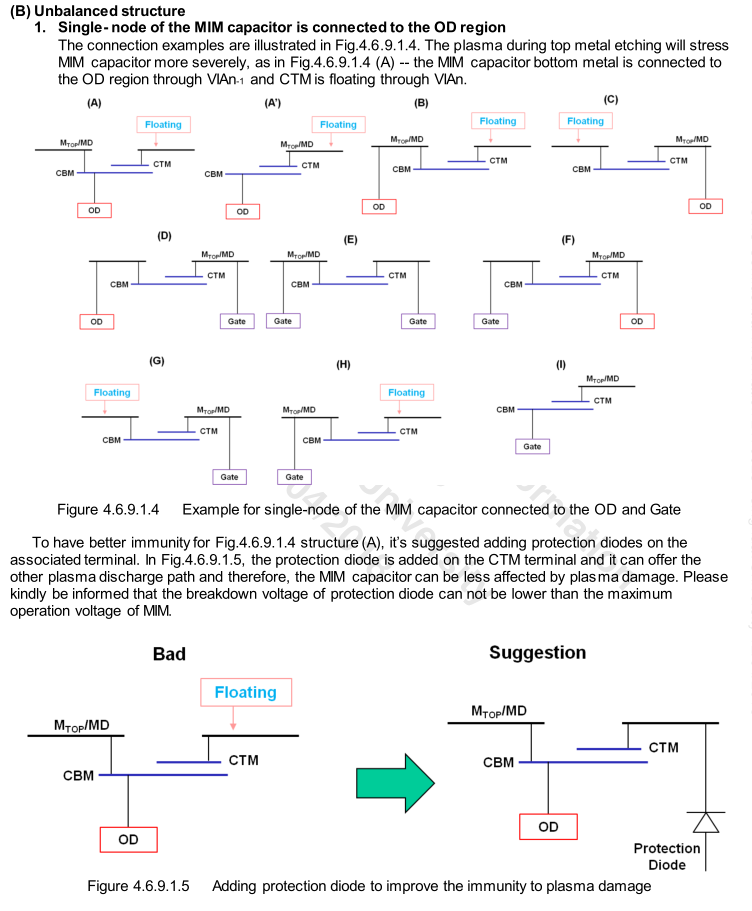

查看官方文档,有那么点理解,但还是不好在版图上下手,增加管子意味着要改电路图,否则lvs过不了,想想这一堆的工作量,直接打退堂鼓。还在鑫韬及时顶上,真加上二极管,消除了不少错误,也让我重新看到希望。

晚上重新回顾这些错误,理了一下,终于豁然开朗:mim的电容的上极板是M6,下极板是M5。M6如果要连其他信号,可以接一个关断的MOS管,用于制造过程中放电;M5如果要连接有源区,需要先跳层到M6,再往下连。电路图如下:

这是M6连接关断MOS管的版图,需要在schematic上添加MOS才能过lvs。小mos管即可,不能影响电容值,比如L=180nm,w=360nm。

这是M6连接关断MOS管的版图,需要在schematic上添加MOS才能过lvs。小mos管即可,不能影响电容值,比如L=180nm,w=360nm。

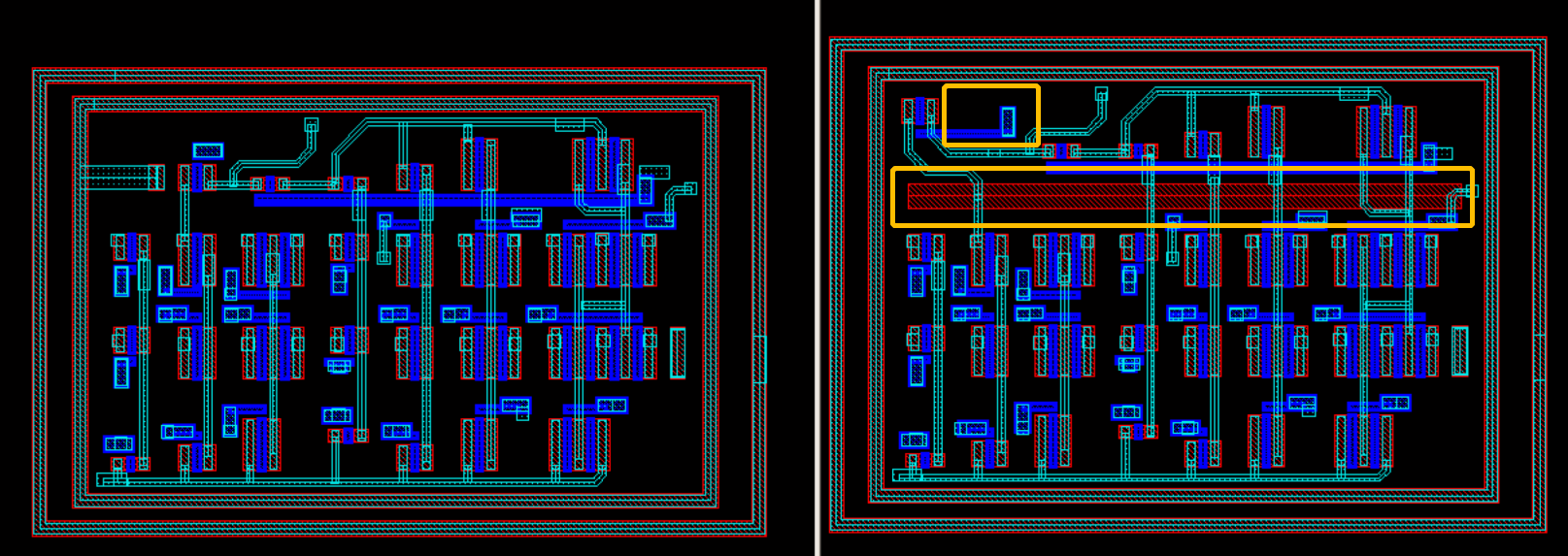

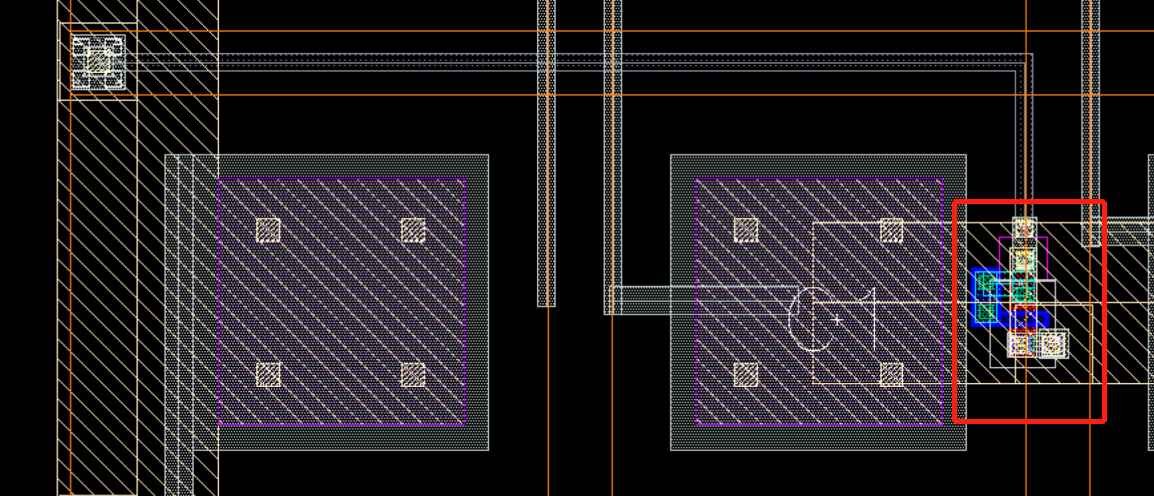

这是M5跳层M6的对比图:

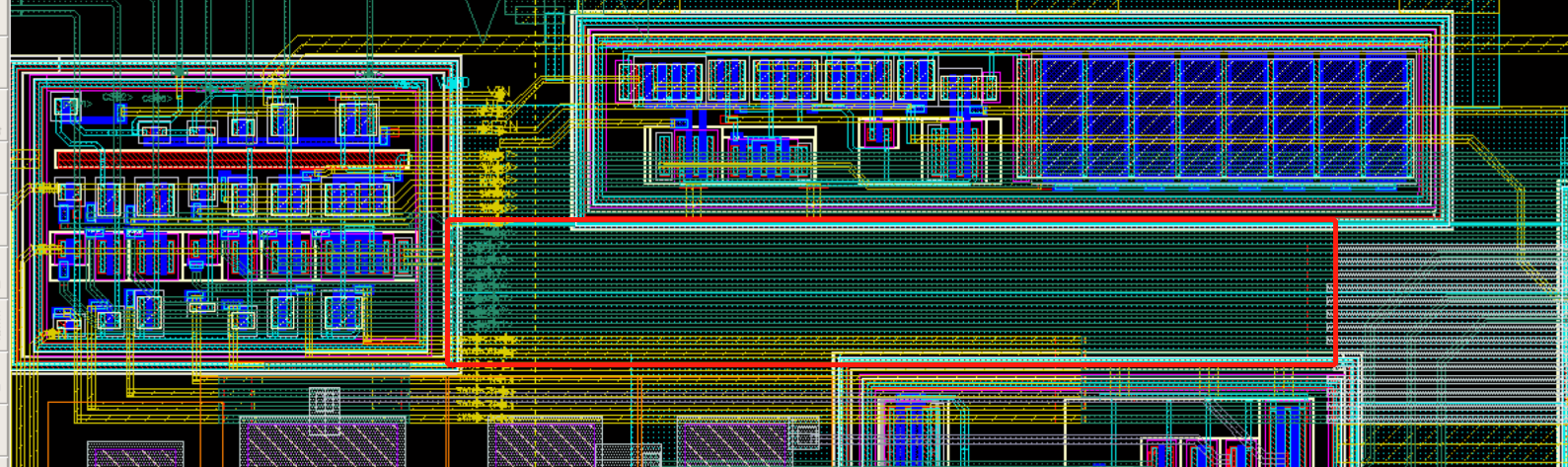

Bug3. A.R.2_A.R.3.M2

这是导线太长导致的错误,文档这样说:

然而我也不懂,一开始就只管切报错的长导线,比如红框部分。但有些奏效,有些不奏效,相当郁闷

然而我也不懂,一开始就只管切报错的长导线,比如红框部分。但有些奏效,有些不奏效,相当郁闷

最后问同学才知道,切的导线要往上跳层,不能往下跳层!下图的红框是,M3跳到M4。

最后问同学才知道,切的导线要往上跳层,不能往下跳层!下图的红框是,M3跳到M4。

Bug4. UTM40K.A.2

这是和dummy金属有关的bug,是dummy脚本的问题,需要手动删除违例的两个金属方块,具体看哪里报错。

三、横扫千军

当各个bug心里有数的时,先改电容阵列的schematic,排除MIM天线电容的错误,再消除导线天线错误,重新生成core的gds,得到dummy版图,拼好之后,最终生成gds。没有忘记后仿,pex提取含pad的R+C+CC寄生参数,仿了2u,30ns周期采样了64个点(输入50*96/1024MHz正弦),ENOB竟然提高到7.94,我相当吃惊,有点受宠若惊。

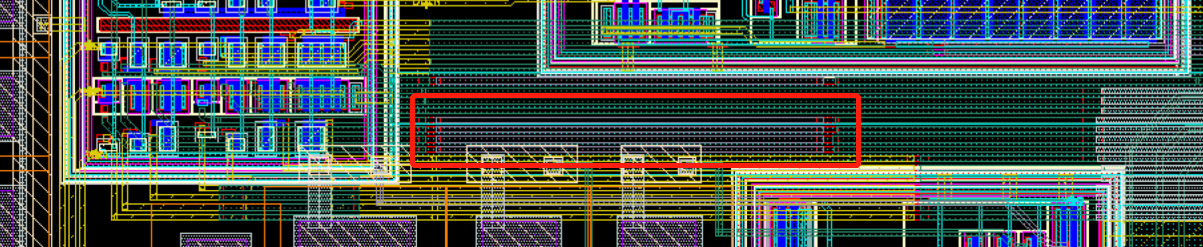

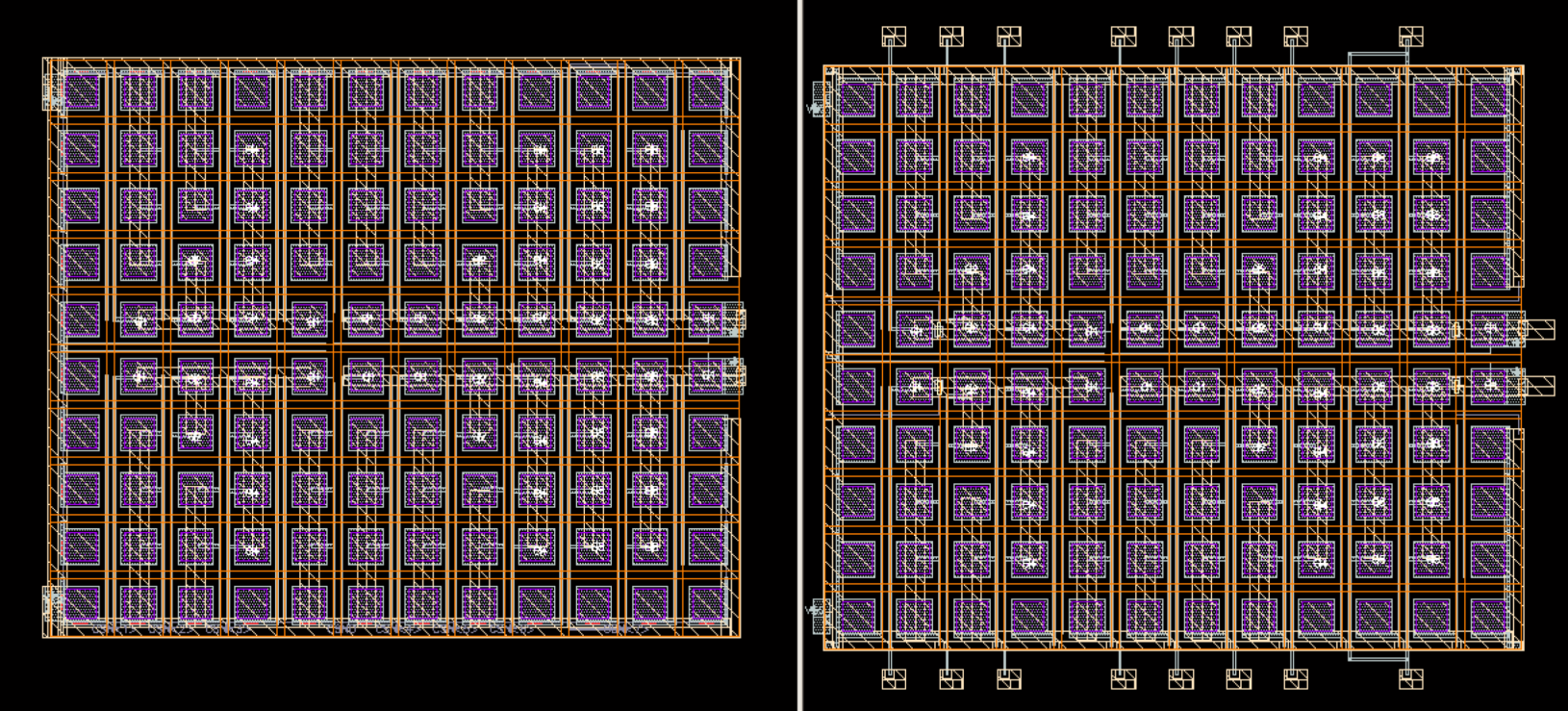

改变最大的是电容阵列,这么多电容都需要跳层:

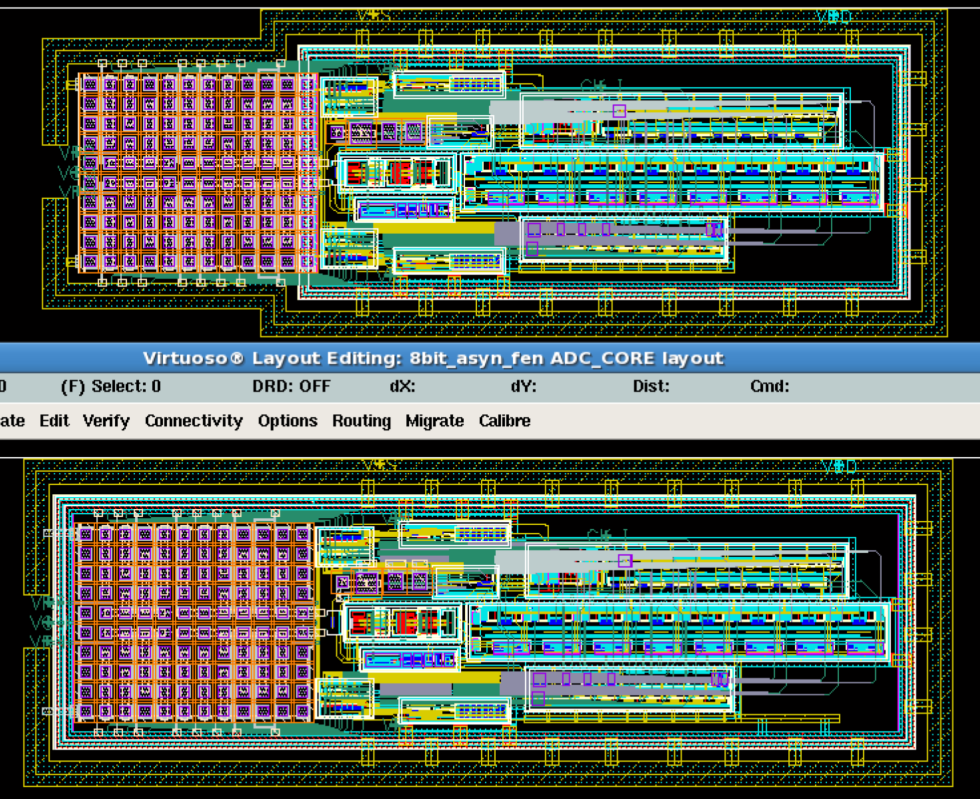

core布局也需要调整位置和连线,和外围的大小:

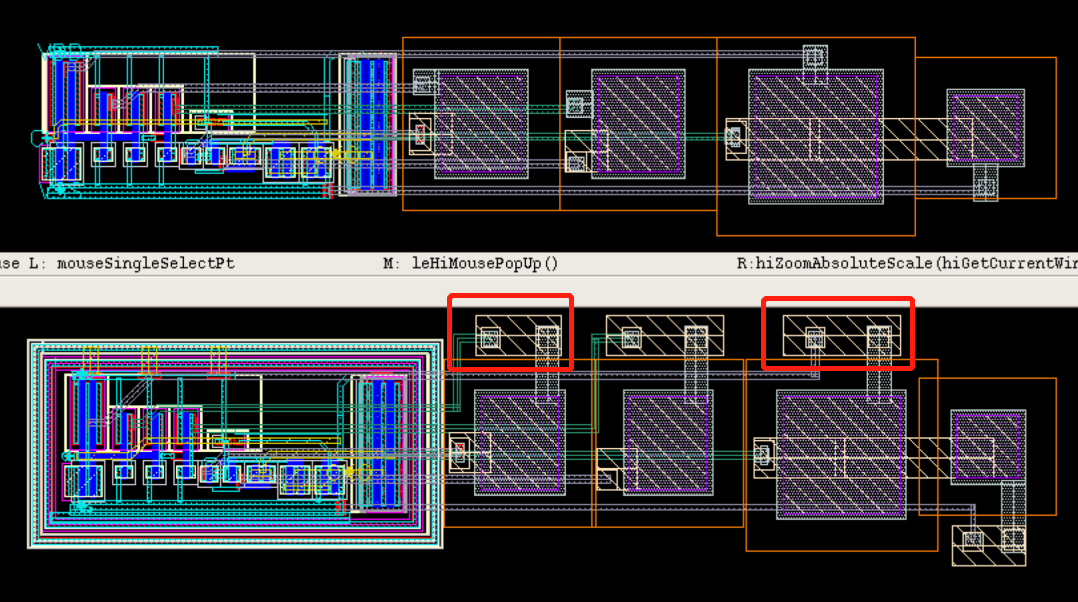

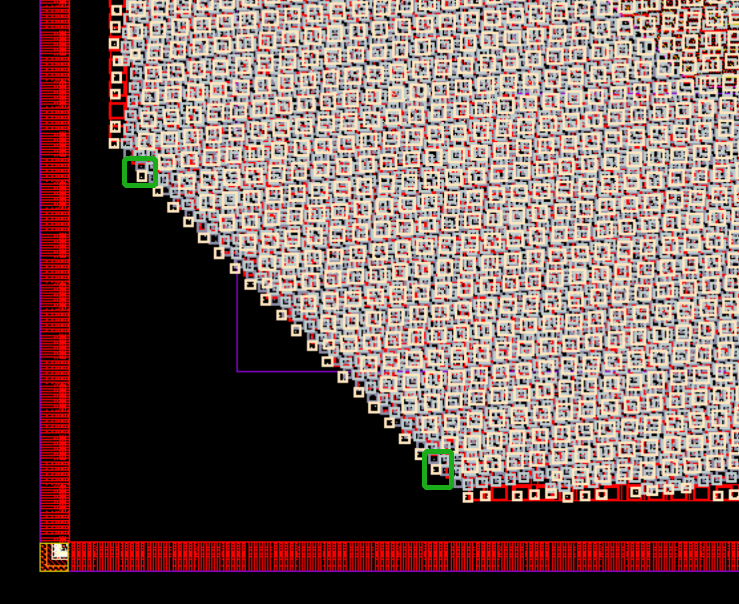

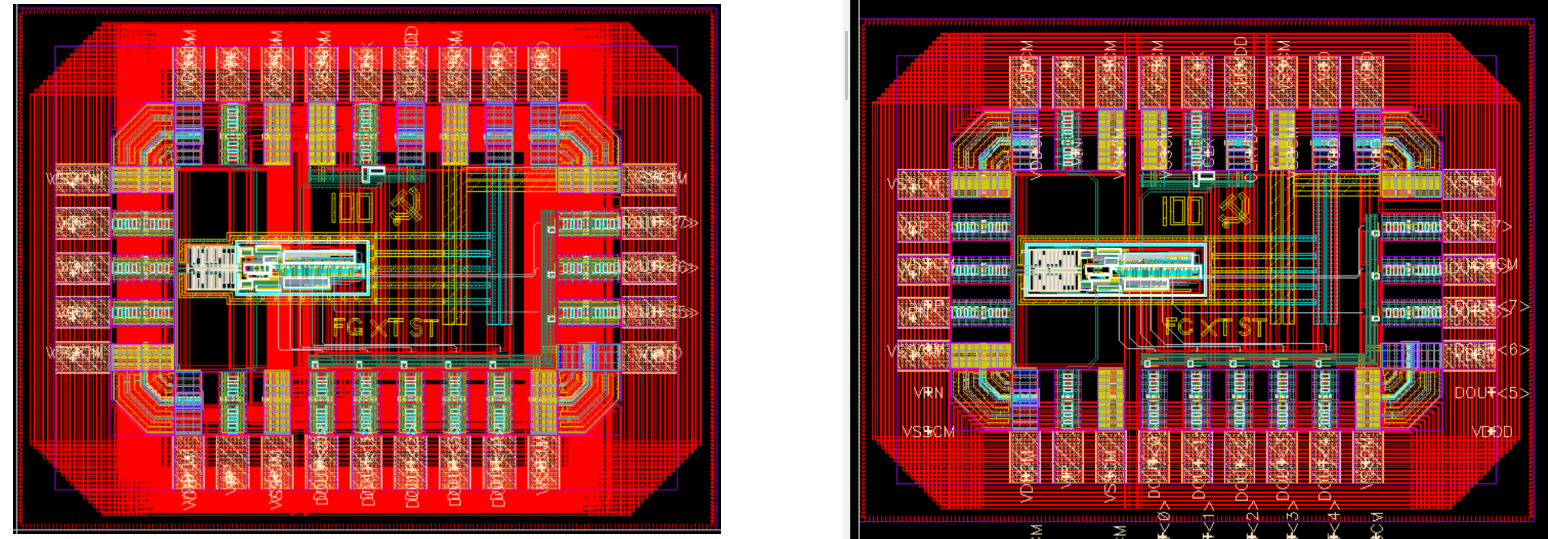

最终的版图远看差别不大,但就是这一点点改变的背后,包含多少内心的折磨、狂喜和平静:

最终的版图远看差别不大,但就是这一点点改变的背后,包含多少内心的折磨、狂喜和平静:

四、后记

模拟IC确实非常靠经验,一个小小的bug,知道的人一句话,不知道的人半天没进展。主要是模拟的bug不好描述,论坛的分享比较少。希望我这又长又臭的debug分享能给别人一些帮助。

太强了大佬 内容很有用 找了很久才找到把问题和解决方法说清楚说明白的 太感谢了!!!!!