Synopsys DC 笔记

一、DC综合概述

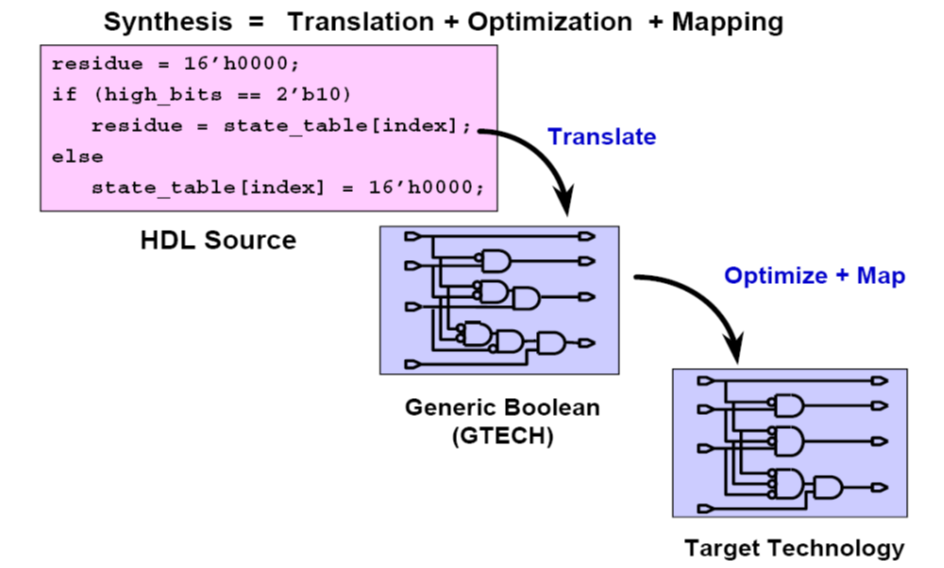

DC(Design Compile)是将行为级(RTL)的源码转换为门级网表的过程。大体上可以分为三个步骤:

综合=转化+逻辑优化+映射

GTECH格式

GTECH格式是DC先将不同语言的RTL网表(如Verilog,VHDL等),转化成统一的与工艺无关的门级网表形式。

转化的过程中,DC会利用其内部的DesignWare库对RTL代码进行结构级和逻辑级的优化。

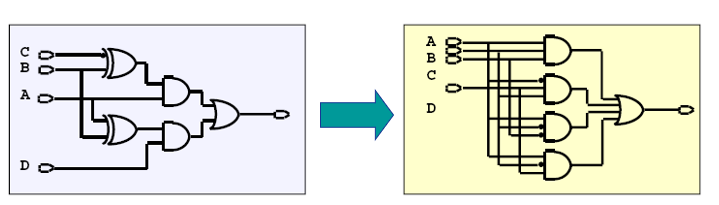

比如,通过共用表达式,进行结构级优化:

通过展平,把组合逻辑路径减少两级,变为乘积之和的电路,进行逻辑优化

约束

下图是经典的时序路径图,设时钟周期为$T_c$,触发器FF3的建立时间为$T_{setup}$,保持时间为$T_{hold}$,触发器FF2的时钟端到Q端的延迟为$T_{clk-q}$,那么时序上应该满足:

$$ \begin{aligned} T_c-T_{setup}&>T_{clk-q}+T_x \\ T_{clk-q}+T_x&>T_{hold} \end{aligned} $$ 或者中间的逻辑单元延时$T_x$应该满足: $$ T_{hold}-T_{clk-q}综合时会在给定约束的情况下,满足时序,并尽量减小面积,即“Optimization”。

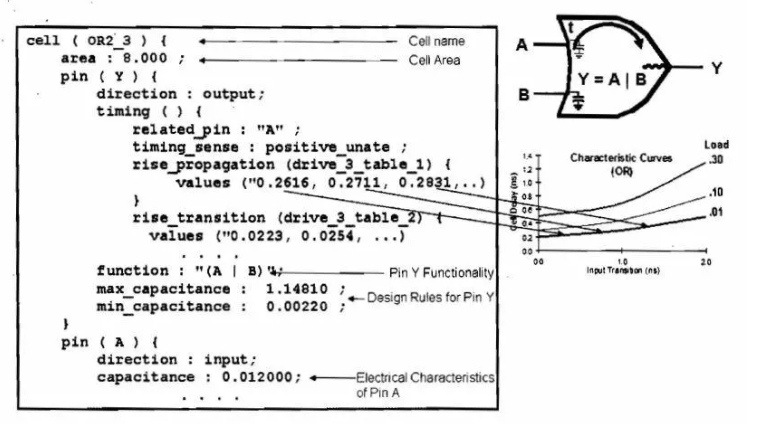

Mapping

Mapping是将工艺库中的逻辑门映射到gtech网表中,工艺库文件后缀一般为.db(database),不能直接打开,需要变为.lib格式,它包含组合单元的时序信息。下图是或门的部分信息:

它包含总面积,输入管脚的电容,最重要的是延迟计算信息,如右边的图表,给定输入转换时间(input Transitopn)和扇出(Load),就能插值得到传输延迟(Cell Delay)和输出转换时间(output Transition)。当前的输出转换时间又可以作为下一级的输入转换时间,这样就可以计算出模块各个单元的延迟。

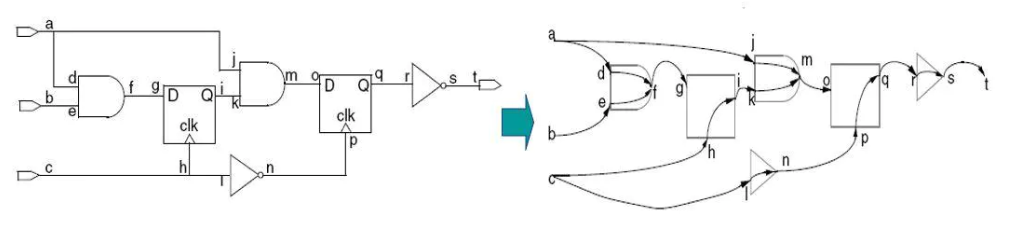

DC在满足时序的条件下,尽量选择工艺库里的小单元以减小面积,最后生成与工艺库相关的逻辑网表。逻辑网表利用IC Compiler工具,加入各个单元的版图信息,布局布线信息,就可以生成版图,送至晶圆厂流片。

二、DC流程

1、设置工艺库文件

- 搜索路径search_path:工艺库文件存放的文件夹,DC会自动在该文件下读入需要的库文件。

- 目标库 target_library:包含基本单元(standard cell),将gtech网表元件映射到具体的工艺单元。

- 链接库 link_libary:包含目标库之外的宏单元、IP核等常用模块。

- 符号库 symbol_library:定义单元的图形库,可以用design_vision查看。

- 综合库 syntehtic_library:是Synopsys公司提供的DesignWare库,包含许多运算单元和IP核,用于产生gtech网表。

2、读入RTL文件

DC支持读入Verilog、VHDL、ddc等格式文件,读入后需要定义顶层模块current_design,并link将读入设计和综合库连接起来。

3、设置约束

设置约束是最重要的一步。

DC判断时序主要看setup time是否满足,hold time需要在IC Compiler 加入版图、布局等信息后更有意义。

DC的判断时序时,会比较data arrival time 和data required time:

- Data arrival time= $T_{clk-q}+T_x$

- Data required time = $T_c-T_{setup} $ 要满足:

4、综合

通过compile_ultra启动DC综合,DC用内建的静态时序工具Design Time来估计路径延迟来指导优化,一般包括三个主要的步骤: 1、把设计分解成时间路径的集合 2、计算每一条路径的延迟 3、所有路径延迟都要检查时序

5、结果输出

输出主要有报告和文件两部分。

- 报告:面积、约束、功耗、时序、违例路径

- 文件:网表文件.v(用于ICC布局布线),约束文件.sdc(用于ICC布局布线),.ddc(保存DC的各种数据)

三、DC注释详解

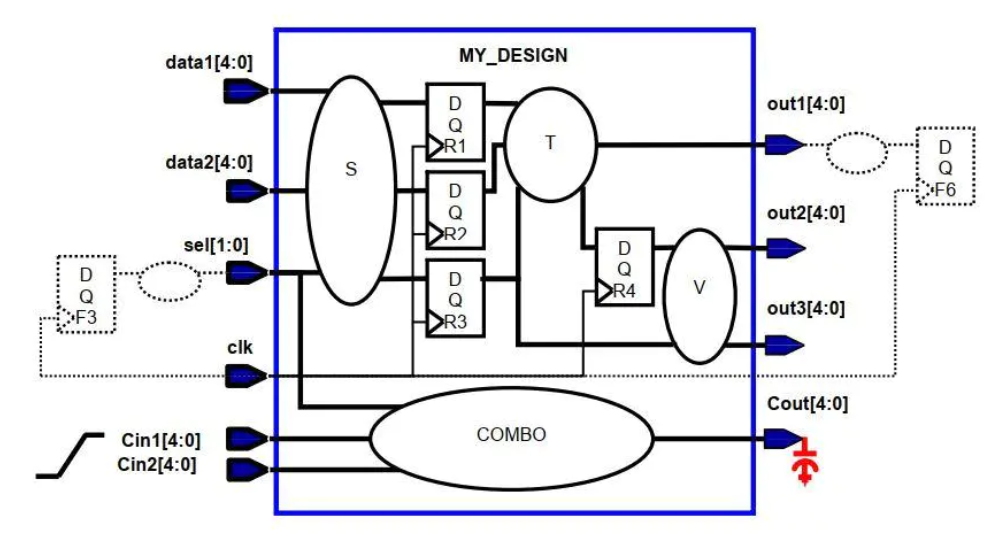

DC的命令采用tcl语言,下面根据synopsys dc lab6的样例写一段综合的脚本。

约束信息来自最初的设计要求:

###################################

# 一、设置工艺库文件 #

###################################

#工艺库文件.db保存在上级目录ref下的db文件夹

#my_design.v文件保存在当前目录rtl下

set search_path "$search_path ../ref/db ./rtl "

#synopsys 内置DesignWare库

set synthetic_library dw_foundation.sldb

set target_library "sc_max.db"

set link_library "* $target_library $synthetic_library"

###################################

# 二、读入RTL文件 #

###################################

read_verilog my_design.v

current_design MY_DESIGN

link

###################################

# 三、设置约束 #

###################################

# 1、时钟设定

# 移除之前的约束

reset_design

#时钟周期3ns

create_clock -period 3.0 [get_ports clk]

#系统时钟到输入端口clk时钟的延迟

set_clock_latency -source -max 0.7 [get_clocks clk]

#输入端口时钟clk到模块内部时钟的延时

set_clock_latency -max 0.3 [get_clocks clk]

#时钟的不确定偏斜时间0.15ns

set_clock_uncertainty -setup 0.15 [get_clocks clk]

#时钟的转换时间0.12ns

set_clock_transition 0.12 [get_clocks clk]

#2、输入延迟设定

#输入端口data1、data2的延迟

set_input_delay -max 0.45 -clock clk [get_ports data*]

#输入端口sel的延迟

set_input_delay -max 0.4 -clock clk [get_ports sel]

#输入端口Cin1、Cin2的延迟

set_input_delay -max 0.3 -clock clk [get_ports Cin*]

#3、输出延迟设定

#输出端口out1的延迟

set_output_delay -max 0.5 -clock clk [get_ports out1]

#输出端口out2的延迟

set_output_delay -max 2.04 -clock clk [get_ports out2]

#输出端口out3的延迟

set_output_delay -max 0.4 -clock clk [get_ports out3]

#输出端口Cout的延迟

set_output_delay -max 0.1 -clock clk [get_ports Cout]

#4、输入转换时间

#输入端口data1、data2、sel的转换时间

set_driving_cell -lib_cell bufbd1 -library cb13fs120_tsmc_max \

[remove_from_collection [all_inputs] [get_ports "clk Cin*"]]

#输入端口Cin1、Cin2的转换时间

set_input_transition 0.12 [get_ports Cin*]

#5、输出负载

#输出端口out1、out2、out3的负载

set_load [expr 2 * [load_of cb13fs120_tsmc_max/bufbd7/I]] [get_ports out*]

#输出端口Cout的负载

set_load 0.025 [get_ports Cout*]

###################################

# 四、综合 #

###################################

compile_ultra

###################################

# 五、结果输出 #

###################################

file mkdir syn_files

file mkdir reports

#报告

#功耗报告

report_power -hierarchy > reports/$DESIGN_NAME.hierarchy.power

report_power > reports/$DESIGN_NAME.power

#面积报告

report_area -hierarchy > reports/$DESIGN_NAME.area

#时序报告

report_timing > reports/$DESIGN_NAME.timing

#约束报告

report_constraint -verbose > reports/$DESIGN_NAME.constraint

#违例报告

report_constraint -all_violators > reports/$DESIGN_NAME.violation

#输出文件

write -h $DESIGN_NAME -output ./syn_files/$DESIGN_NAME.db

write_file -format ddc -hierarchy -output ./syn_files/$DESIGN_NAME.ddc

#SDF格式的延迟,用于Verilog仿真

write_sdf -context verilog -version 1.0 ./syn_files/$DESIGN_NAME.syn.sdf

#Verilog门级网表,用于ICC

write -h -f verilog $DESIGN_NAME -output ./syn_files/$DESIGN_NAME.syn.v

#SDC格式的约束, 用于ICC

write_sdc ./syn_files/$DESIGN_NAME.sdc

最后附送synopsys的实验大礼包,enjoy~

链接:https://pan.baidu.com/s/1XZEVD4MzoFI2Q1mwrFfO6Q 提取码:6666