IP,SoC,SiP和Chiplet的区别

最近经常听到Chiplet的概念,据说AMD的锐龙系列就是利用chiplet技术逆袭Intel的。那么chiplet和SoC,SiP,IP核等有什么关系呢?找了不少资料,特来总结一番。其实这些概念的出现有一个共同的主线,让IC设计和制造越来越容易。

一、IP

早期的复制电路都是全定制,比如Intel的4004cpu,这种设计非常耗时。考虑到cpu的很多模块有相似的地方,能不能把这些东西模块化?于是就有了IP核的概念,Intelligent Property,即知识产权核。

IP核在EDA上有非常重要的地位,我们熟知的Synopsys公司就是IP巨头,它将一些复杂的功能模块,如FIR滤波器、SDRAM控制器、PLL锁相环等封装好,供开发者直接调用,避免重复劳动,他们会收取相应的专利费。ARM公司本质上就是买IP核。

IP核分成三类:软核、固核与硬核。软核就是我们通常写的verilog行为描述代码,灵活性与适应性较强;固核是门级网表形式的代码,是IP的主流形式之一;硬核是GDSII版图文件,不能修改。

二、SoC

SoC(system on chip)片上系统。我们台式机的存储器、电源模块、功耗管理模块等都是分开的,而SoC是将这些围绕CPU的关键模块集成在一个芯片上,这样才会有我们的笔记本、手机等小巧强大电子设备。

SoC强调整体设计,包含总线架构、IP核复用、软硬件协同设计、低功耗等技术,将CPU、存储器、各种接口控制模块、互联总线等集成在一起,达到减小面积、提高速度、降低功耗、节约成本等目的。

三、SiP

SiP(System-in Package)系统级封装。将处理器、存储器、FPGA等功能芯片集成在一个封装内。粗粗一看,似乎和SoC一样,但区别还是挺大的。

SoC是在同一芯片、同一钟工艺下完成的;SiP则可以将不同工艺器件,如MEM、光学器件、射频器件等不同材质、不同工艺节点的设备垂直堆叠或水平排列,做园片级别的封装。这是超越摩尔定律的重要实现路径。

SiP的实现需要多种封装技术,如引线键合、倒装芯片、芯片堆叠、基板腔体、基板集成RF器件、埋入式电阻\电容\电感、硅通孔TSV等。

四、Chiplet

Chiplet即小芯片,相当于将硬核IP再制造成芯片。还是回到SoC,随着工艺节点的推进,成本越来越昂贵,SoC会增大芯片面积,导致良品率下降,成本很高。这时候,AMD给了新方案Chiplet。

7nm工艺时,模拟电路无法获益于晶体管或导线间距的微缩,传递信号的I/O本身凸块间距微缩进展缓慢,用14nm工艺还更加稳定。

cpu也进入多核时代,将这些核独立制造可以大大提高良率。

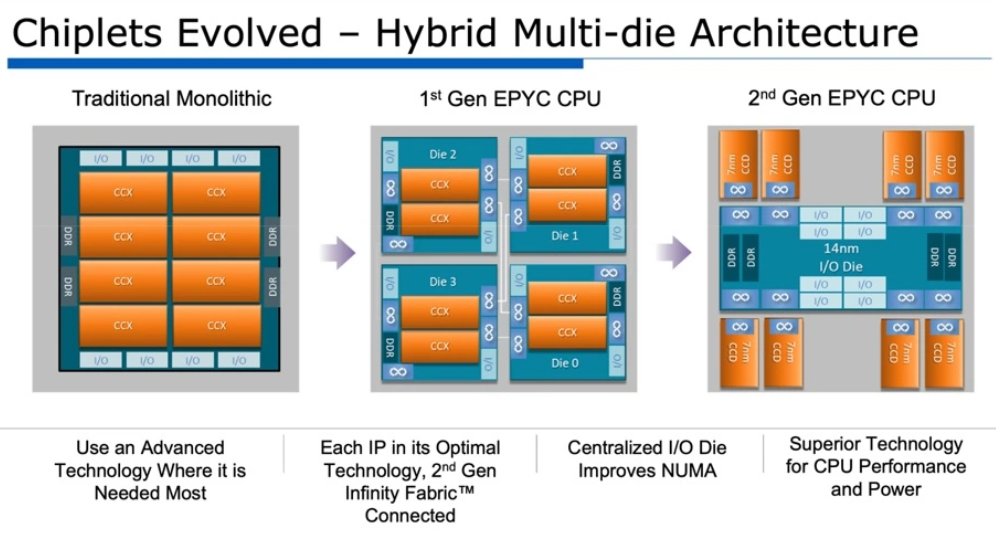

如图,这是AMD的CPU设计演进图,从单芯片到小芯片组合,到模拟、I/O采用14nm工艺,整个成本节省了41%。

能达到这样的效果,要归功于SiP先进的封装技术。

您好,我是IP与SoC设计公众号的编辑,想转载您的《IP,SoC,SiP和Chiplet的区别》一文,注明作者及出处,请问您是否愿意呢?

可以吧